垂直方向へのスケーリングは3次元で行われるため、半導体プロセスの開発や制御において3D分析が非常に重要です。

最先端の3D解析方法は、断面を測定することです。これは時間がかかり、サンプリングが面倒で点ごとの解析を行うため、精度に制限があります。

当社の革新的な測定用テストチップとウェハは、測定の速度、精度、およびコストを改善するために設計されています。

Chipmetricsでは、半導体プロセス制御のための革新的な測定チップとウェハを提供しています。

当社の最先端ソリューションの応用分野は、薄膜プロセスの開発、ツールの均一性評価、半導体および先進材料製造全般の品質保証にあります。

当社は、3Dの高アスペクト比テスト構造を使用した薄膜の均一性測定における第一人者です。

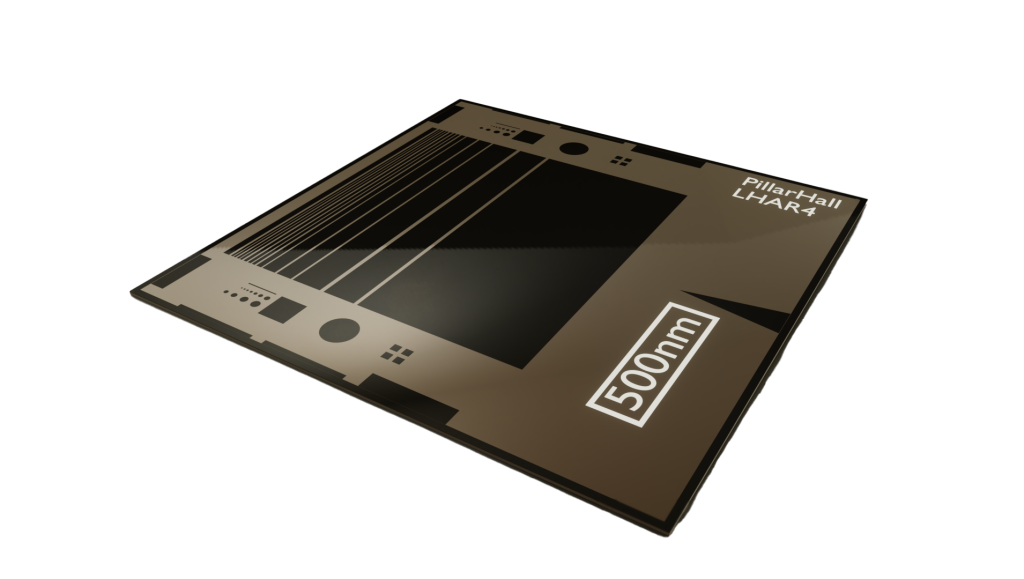

PillarHall LHAR4シリコンテストチップには、ALDおよびCVD薄膜の特性評価のための横方向超高アスペクト比テスト構造(>1000)が含まれています。これは、深いトレンチ内での薄膜の均一性と薄膜の側壁特性を測定するツールとして使用されます。

アプリケーション

分析プロセス

Chipmetricsのポケットウェハの目的は、Chipmetricsのテストチップをウェハレベルの処理でより簡単に使用できるようにすることです。エッチングされたポケットを持つポケットウェハは、複数の15×15 mmテストチップを収容するように設計されています。利用可能なポケットウェハのサイズは、150 mm、200 mm、および300 mmです。

Chipmetrics垂直高アスペクト比(VHAR1)シリコンテストチップは、垂直のな高アスペクト比のホールの配列で構成されています。これらのホールは、チップ全体の面積15×15mmにわたって、一定の直径1µm、深さ200µmとなっています。

Chipmetricsの測定サービスは、膜の浸透深さプロファイルデータを提供します。このサービスは、Chipmetrics PillarHall® LHAR4テストチップ上で堆積されたサンプルフィルムが測定可能であることが必要です。

サービスプロセス

Chipmetricsは2024年の日本応用物理学会春季学術講演会に参加しています。この参加は、日本の科学技術コミュニティとのつながりを深めるという当社の取り組みを示しています。

ChipmetricsチームのCTOであるFeng Gaoが、学術講演会でポスター発表を行います。Fengのプレゼンテーションでは、私たちの最新の研究開発成果を紹介し、「Thin-Film Conformality: An Integration of LHAR Structures with Optical Techniques」についての見解を述べます。

Chipmetricsは、ALD/ALE2024イベントのゴールドスポンサーとして参加をします。特に今年は、フィンランドでの発明以来の原子層堆積(ALD)技術の50周年を祝う重要な年です。

私たちは、全てのALDの専門家、研究者、および学生の皆様をフィンランドで開催されるこの国際学会に温かく迎え入れます。見解に満ちたプレゼンテーションと、分野の先駆者や現在のイノベーターとのネットワークを築く機会が満載です

電話: +358 10 348 1344

電子メール: [email protected]

最高のエクスペリエンスを提供するために、当社では Cookie などのテクノロジーを使用してデバイス情報を保存またはアクセスします。 これらのテクノロジーに同意すると、このサイトの閲覧行動や固有の ID などのデータを処理できるようになります。 同意しない、または同意を撤回すると、特定の機能に悪影響を及ぼす可能性があります。